TP11

- fonctions et portes logiques

Il

s'agit d'une correction partielle.

1/

Résultats principaux sur les portes : TV, symboles,

fonction et désignation en technologie CMOS.

On

utilisera de

préférence les symboles

américains, plus facilement identifiables sur un schéma.

Simulation des portes logiques : http://www.univ-lemans.fr/enseignements/physique/02/electro/portes.html

2/

Addtion binaire

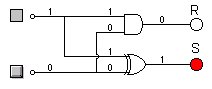

2.1. Demi-additionneur

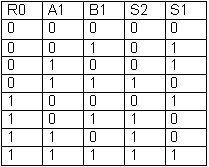

| TV |

montage |

expressions

logiques |

|

|

R

= A0 and

B0

S = A0 xor B0 |

Cliquer

pour voir une photo du montage sur platine mille trous.

Le

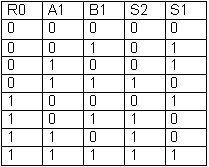

montage doit faire apparaître un ½ additionneur

(pour

ajouter les bits de rang 0) et un addtionneur complet (pour ajouter les

bits de rang 1 et l'éventuelle retenue provenant du rang 0).

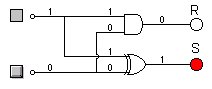

| TV |

montage |

|

|

2.4.

Additionneur 4 bits

Cliquer

pour une photo de la

plaquette